Electrical and Thermal Modeling for Heterogeneous Integration

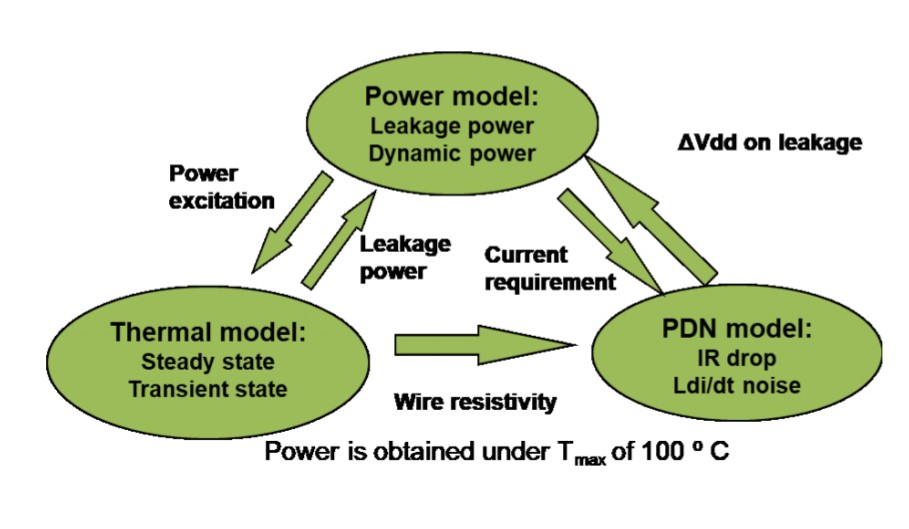

There is an exploding interest in heterogeneous integration of multi-functional chiplets into a single package using 2.5D/3D technologies, such as high-bandwidth memory with GPUs, field programmable gate arrays (FPGAs) with server processors, and high-performance GPUs with general-purpose CPUs. These high-performance integrated systems inevitably lead to higher current demand and increased power density as the power supply voltage is scaled down in recent technology nodes. As a result, the power delivery in high-performance digital systems is an increasingly difficult challenge. Therefore, before taking full advantage of emerging 2.5-D and 3-D integration platforms, we need to first address the challenges of power delivery network (PDN) and power supply noise (PSN). PDN and PSN in traditional single-chip packages have been extensively studied in the literature. However, 2.5D and 3D integrated electronics present very unique challenges that require careful design considerations. Even more, PSN has very strong interdependence on temperature, and thus requiring thermal-PDN co-design and optimization for emerging 2.5D and 3D heterogeneous integration including back-side power delivery.